基于異構多核架構的全高清H.264解碼系統(tǒng)網(wǎng)絡化工程設計與實現(xiàn)

隨著多媒體應用的普及和高清視頻需求的爆發(fā)式增長,高效、實時的視頻解碼系統(tǒng)成為數(shù)字處理領域的關鍵。基于異構多核處理器(如ARM + DSP/GPU/FPGA組合)的全高清H.264解碼系統(tǒng),以其優(yōu)異的性能功耗比和靈活性,成為解決這一挑戰(zhàn)的主流方案。本文將探討此類解碼系統(tǒng)的核心設計,并重點闡述其在網(wǎng)絡系統(tǒng)工程中的集成與設計考量。

一、 異構多核H.264解碼系統(tǒng)核心架構設計

- 處理器選型與任務劃分:

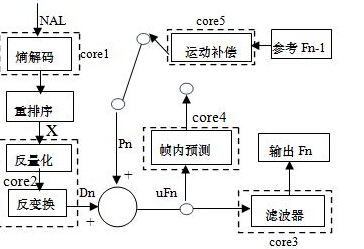

- 控制核心:通常選用高性能、低功耗的ARM Cortex-A系列處理器,負責系統(tǒng)控制、任務調(diào)度、網(wǎng)絡協(xié)議棧處理、用戶交互及碼流解析(如NAL單元解析、序列參數(shù)集/圖像參數(shù)集解碼)。

- 計算核心:針對H.264解碼中計算密集型的模塊(如熵解碼、反量化、反變換、運動補償、去塊濾波),采用專用計算單元。例如,使用DSP進行高效的定點運算,利用GPU的并行處理能力進行宏塊級或幀級并行解碼,或采用FPGA實現(xiàn)高度定制化的流水線處理。這種異構分工充分發(fā)揮了各核的優(yōu)勢。

- 存儲子系統(tǒng)設計:

- 采用層次化存儲結構,包括片上高速緩存(L1/L2)、共享內(nèi)存和外部DDR。需精心設計數(shù)據(jù)布局,減少核間數(shù)據(jù)搬運開銷,尤其是參考幀、當前幀數(shù)據(jù)在ARM與加速核之間的高效傳遞。

- 核間通信與同步機制:

- 基于共享內(nèi)存、郵箱寄存器或高速總線(如AXI)實現(xiàn)。設計高效的消息傳遞或數(shù)據(jù)流模型,確保解碼任務流水線的順暢,避免處理單元因等待數(shù)據(jù)而空閑。

二、 解碼算法在異構平臺上的并行化與優(yōu)化

- 功能級并行:將解碼流程(如熵解碼、重排序、宏塊解碼)映射到不同的處理單元,形成流水線。

- 數(shù)據(jù)級并行:在GPU或眾核DSP上,對幀內(nèi)多個宏塊或切片(Slice)進行并行解碼,這是提升全高清(1080p)解碼速率的關鍵。

- 指令級優(yōu)化:針對特定計算核心(如DSP的SIMD指令集)對關鍵算法(如IDCT、運動補償插值)進行深度優(yōu)化。

三、 網(wǎng)絡系統(tǒng)工程集成設計

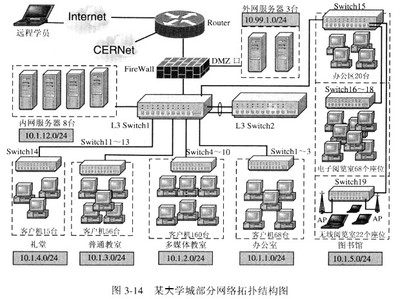

將上述異構解碼系統(tǒng)作為網(wǎng)絡中的一個智能節(jié)點進行設計,需考慮以下層面:

- 網(wǎng)絡接口與協(xié)議處理:

- 在ARM控制核上集成以太網(wǎng)MAC/PHY或無線網(wǎng)絡模塊(如Wi-Fi)。

- 實現(xiàn)完整的TCP/IP協(xié)議棧,并針對實時視頻流優(yōu)化UDP/RTP協(xié)議的處理。支持RTSP用于點播控制,或TS over UDP/IP用于廣播流接收。

- 設計網(wǎng)絡抖動緩沖區(qū)和丟包重傳/錯誤隱藏機制,保障解碼的連續(xù)性與實時性。

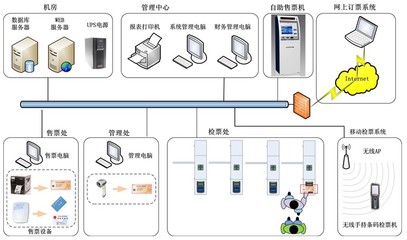

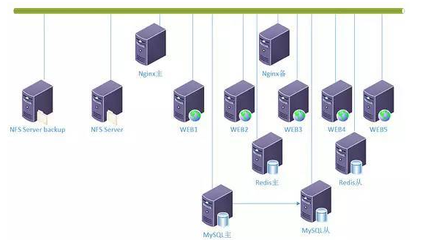

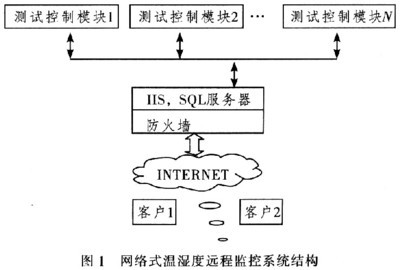

- 流媒體服務與客戶端架構:

- 服務器端:系統(tǒng)可作為嵌入式流媒體服務器,從存儲設備或前端采集器獲取H.264碼流,通過網(wǎng)絡協(xié)議分發(fā)給多個客戶端。

- 客戶端端:系統(tǒng)作為播放終端,接收網(wǎng)絡碼流,送入異構解碼流水線,解碼后的幀緩沖通過顯示控制器輸出。

- 需設計高效的數(shù)據(jù)通路:

網(wǎng)絡接口 → DMA → 內(nèi)存(碼流緩沖區(qū))→ ARM(協(xié)議解析、調(diào)度)→ 共享內(nèi)存/直接通路 → 計算核心(解碼)→ 幀緩沖區(qū) → 顯示輸出。

- 系統(tǒng)管理與監(jiān)控:

- 實現(xiàn)基于Web或專用協(xié)議的遠程管理接口,允許網(wǎng)絡管理員配置解碼參數(shù)、查看系統(tǒng)狀態(tài)(如CPU負載、網(wǎng)絡帶寬、解碼幀率)。

- 設計看門狗和故障恢復機制,確保系統(tǒng)在網(wǎng)絡異常或局部失效時能保持穩(wěn)定或快速重啟。

- 功耗與熱管理:

- 在網(wǎng)絡負載和解碼任務變化時,動態(tài)調(diào)整各核的工作頻率與電壓(DVFS),關閉空閑模塊,以降低整體功耗,這對于大規(guī)模部署的網(wǎng)絡系統(tǒng)工程尤為重要。

四、 挑戰(zhàn)與展望

設計此類系統(tǒng)的主要挑戰(zhàn)在于:軟硬件協(xié)同設計的復雜性、核間通信與數(shù)據(jù)一致性的開銷、網(wǎng)絡延遲與解碼實時性的平衡,以及多版本H.264碼流(如High Profile)的兼容性。隨著編解碼標準向H.265/HEVC、AV1演進,以及AI增強視頻處理需求的興起,異構多核系統(tǒng)的設計需要更高的可編程性和智能化任務調(diào)度能力,并與邊緣計算、5G網(wǎng)絡更深度地融合,以構建更高性能、更低延遲的分布式視頻處理網(wǎng)絡系統(tǒng)工程。

基于異構多核的全高清H.264解碼系統(tǒng)設計,是一個跨越芯片架構、視頻算法、操作系統(tǒng)和網(wǎng)絡通信的綜合性工程。成功的網(wǎng)絡系統(tǒng)工程實現(xiàn),不僅要求解碼內(nèi)核的高效,更依賴于整個數(shù)據(jù)鏈路與網(wǎng)絡接口的優(yōu)化設計,從而在復雜的網(wǎng)絡環(huán)境中提供穩(wěn)定、高清、實時的視頻服務。

如若轉載,請注明出處:http://m.decj.cn/product/35.html

更新時間:2026-04-06 23:59:10